11.6.2.1 : Le matériel

Pour les premières études de principe, le FPGA choisi a été celui fourni par la carte de développement DE1-SoC [165]Terasic: DE1-SoC board. Sur cette carte, le FPGA contient sur la même puce un vrai (hard) processeur ARM Cortex A9 avec 2 cœurs, formant ce qu'on appelle un System on Chip (SoC). Avec une mémoire permanente amovible sous la forme d'une carte Micro-SD, le tout peut accueillir un système d'exploitation Linux. Pour les applications OpenCL, il existe une passerelle directe entre le microprocesseur ARM et le FPGA.

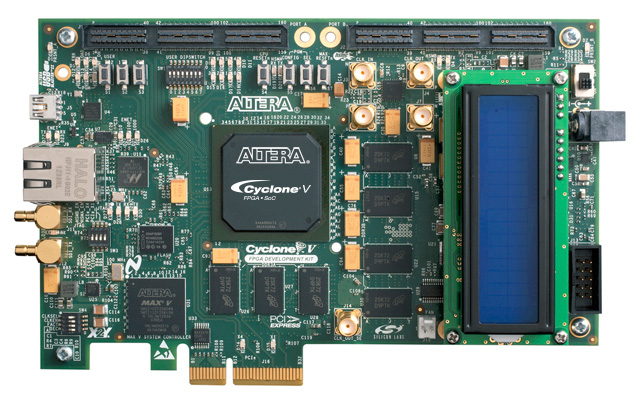

![]() Figure 48 : La carte de développement DE1-SoC assemblée et vendue par l'entreprise Terasic, contient un FPGA Cyclone V SE 5CSEMA5F31C6N

Figure 48 : La carte de développement DE1-SoC assemblée et vendue par l'entreprise Terasic, contient un FPGA Cyclone V SE 5CSEMA5F31C6N

Cette carte (figure 48) est un outil de laboratoire pour de nombreuses études qui impliquent l'utilisation d'un FPGA~: des applications audio, vidéo, robotique, capteurs et autres périphériques (LEDs, interfaces de données) et le fabricant offre un nombre de projets pour démarrer dans la programmation HDL d'un FPGA. La carte s'alimente séparément et peut recevoir un écran, un clavier et une souris, afin de travailler sur le système installé dessus.

La compilation d'un projet OpenCL doit se faire sur un PC avec beaucoup plus de ressources que cette carte, car il faut d'abord installer Quartus (qui occupe à l'installation quelques dizaines de giga-octets). Ici il faut aussi installer le SDK OpenCL. Sur le système installé sur la carte DE1-SoC, nous avons besoin du pilote OpenCL pour le FPGA (compilé comme module dans le noyau Linux) et du RTE OpenCL. La compilation de la partie hôte du code (pour une architecture ARM) peut se faire avec un compilateur croisé (cross compiler) et à la fin l'exécutable et l'image FPGA seront transférés vers le système sur la DE1-SoC à travers le réseau Ethernet. Le RTE du OpenCL offre aussi un outil pour charger l'image binaire sur le FPGA de la DE1-SoC.

Cette première version de travail a été très utile pour valider la méthode, mais elle reste inadaptée comme solution d'accélération sur une architecture de calcul habituelle. L'idée est d'avoir accès au FPGA directement depuis le PC hôte et ceci est possible avec un autre type de cartes, qui sont montée sur la passerelle PCIe (Peripheral Component Interconnect). Cette connexion assure l'alimentation de la carte, l'échange des données entre la mémoire du PC hôte et la mémoire accessible par le FPGA et même le chargement de l'image binaire sur le FPGA.

Il a été précisé auparavant que pour développer un projet OpenCL sur un FPGA nous avons besoin d'une image de base (BSP) qui contient déjà les circuits de base et d'interfaçage pour pouvoir configurer les noyaux OpenCL selon les spécifications du code. Pour la carte DE1-SoC, le fabricant met à disposition un BSP pour la version 16.0 de Quartus (et du SDK OpenCL), la dernière avant l'acquisition d'Altera par Intel. Ça signifie qu'on ne peut pas exploiter cette carte avec des versions ultérieures du SDK. Pour la carte Cyclone V GT (figure 49), montable sur le PC hôte par un connecteur PCIe, le seul BSP trouvé a été celui crée par un développeur FPGA (Sethuraman Kuppuswamy [166]Cyclone V GT: board support package for Intel FPGA SDK OpenCL), mis en ligne en mai 2017, pour la version 17.0 du SDK OpenCL (la version la plus récente est 18.1). Depuis, la situation a évolué et dans une autresection nous allons montrer quelles sont les configurations actuellement privilégiées par Intel, en tant que fabricant de FPGA, par son Programming Solutions Group.

Le FPGA de la deuxième carte est aussi plus performant que celui de la carte DE1-SoC. Le tableau 3 montre quelques caractéristiques des deux FPGA utilisés. Quelques aspects essentiels pour la capacité liée à la programmation OpenCL en ressortent~:

- le nombre d'éléments logiques donne la capacité d'insérer des circuits hardware logiques et de les connecter selon le flux de données explicité dans le code~; ceci s'exprime aussi en nombre de registres, de modules flexibles ALM (Adaptive Logic Module) et de bascules FF

- en plus des éléments logiques, des structures plus spécialisées déjà insérées dans la structure du FPGA, comme les DSP ou les multiplicateurs, peuvent être utilisés dans la synthèse du noyau OpenCL en image hardware

- le grade de rapidité est en relation avec la vitesse de commutation des circuits de type bascule FF, c'est-à-dire avec la vitesse de fonctionnement du FPGA en général~: plus bas l'indice, plus rapide le FPGA

- le FPGA dispose d'une mémoire interne, organisé en petits blocs de mémoire répartis sur la surface du FPGA pour optimiser les accès~; le standard OpenCL manipule les données en trois niveaux hiérarchiques de mémoire~: globale, locale et privée, en fonction du temps d'accès, le partage et le contrôle des opérations d'accès par des barrières

[t]

| Caractéristique | Carte DE1-SoC | Carte Cyclone V GT |

| [5pt] Code FPGA | 5CSEMA5F31C6N | 5CGTFD9E5F35C7N |

| [5pt] System on chip (SoC) | oui | non |

| [5pt] Processeur hard | ARM Cortex A9 | - |

| [5pt] IP hard pour contrôle de mémoire | 1 | 2 |

| [5pt] IP hard pour connexion PCIe | 0 | 2 (PCIe x4) |

| [5pt] Nombre d'éléments logiques (LE) | 85k | 301k |

| [5pt] Nombre de connecteurs | 896 | 1152 |

| [5pt] Grade de rapidité | 6 | 7 |

| [5pt] Mémoire interne (M10K) | 3970 | 12200 |

| [5pt] DSP de précision variable | 87 | 342 |

| [5pt] Multiplicateurs 18x18 | 174 | 684 |

| [5pt] Prix [Euro] | 250 | 1100 |

| [5pt] |

![]() Table 3 : Un extrait des caractéristiques des deux FPGA en test~: DE1-SoC et Cyclone V GT [157]Cyclone V Device Overview, Intel

Table 3 : Un extrait des caractéristiques des deux FPGA en test~: DE1-SoC et Cyclone V GT [157]Cyclone V Device Overview, Intel

La carte Cyclone V GT est montée sur la carte mère du PC hôte dans une prise PCIe libre (elle peut être plus large que $\times$ 4) et ensuite un câble USB doit relier l'entrée de programmation JTAG de la carte (visible en extérieur à l'arrière du PC) avec une prise USB du même PC hôte. Ce câble servira au chargement de l'image binaire FPGA obtenue après la compilation, qui se fera au moment de l'exécution du code hôte par l'appel d'une commande Quartus. Avec la BSP disponible (voir plus haut) il n'est pas possible de charger cette image par la passerelle PCIe, aspect qui diminue la vitesse de chargement, mais, vu que pour une seule tâche de calcul avec un seul noyau compilé l'image est transféré une seule fois au début, la performance de calcul n'est pas altérée.